嵌入式面试常见问题整理

基本概念

单工,半双工,全双工

- 单工:简单的说就是一方只能发信息,另一方则只能收信息,通信是单向的。

- 半双工:比单工先进一点,就是双方都能发信息,但同一时间则只能一方发信息。

- -全双工:比半双工再先进一点,就是双方不仅都能发信息,而且能够同时发送。

FLASH 和 EEPROM区别

基本概念:

- ROM: Read-Only Memory

- RAM: Random Access Memory

- FLASH: Flash 存储器(FLASH EEPROM)又称闪存,快闪。它是EEPROM的一种。它结合了ROM和RAM的长处。不仅具备电子可擦除可编辑(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据

- EEPROM: Electrically-Erasable Programmable Read-Only Memory

- SRAM:静态RAM,读写速度非常快,比较昂贵。一般用于CPU的一级缓冲,二级缓冲。

- DRAM:动态RAM,DRAM保留数据的时间很短,速度比SRAM慢,但是比任何ROM快。计算机的内存是DRAM。

FLASH和EEPROM的最大区别是FLASH按扇区操作,EEPROM则按字节操作,二者寻址方法不同,存储单元的结构也不同,FLASH的电路结构较简单,同样容量占芯片面积较小,成本自然比EEPROM低,因而适合用作程序存储器,EEPROM则更多的用作非易失的数据存储器。

目前的单片机,RAM主要是做运行时数据存储器,FLASH主要是程序存储器,EEPROM主要是用以在程序运行保存一些需要掉电不丢失的数据.

- Nano Flash和NOR Flash的区别:

目前Flash主要有NANO和NOR两种

- NOR Flash:该种Flash的读写和创建的SDRAM读写一样,用户可以直接运行装载在NOR Flash里面的代码,这样可以减少SRAM的容量从而节约成本。

- NANO Flash:NAND Flash没有采取内存的随即读取技术,它的读取是一次读取一块的形式来进行的,通常是一次读取512个字节,采用这种技术的Flash比较廉价,用户无法直接运行上面的代码。

总线协议

CAN总线协议(Controller Area Network)

CAN总线协议是由博世开发的一种基于消息广播模式的串行通信总线,该协议非常适合于现场控制领域,主要用于实现汽车ECU之间的可靠通信。该通讯协议最高速率可达到1Mbps, 容错能力强。CAN控制器包含强大的检错和处理机制。另外CAN的节点之间不会传输大数据块,一帧CAN消息最多传输8字节用户数据。

总线特点

- 多主控制,总线空闲时所有单元都可以发送消息,最先访问总线的单元获得发送权,多个单元同时发送时,发送优先级高的可以发送。发送的消息保温不包含原地址和目标地址,只通过标识符表示消息的功能和优先级。

- 总线为事件触发型,只有消息要发送时,节点才向总线上广播消息; 同时每个节点也可以通过发送远程帧请求其他节点发送数据。

- 总线上可同时连接多个节点,可连接节点总数在理论上是没有限制的,实际可连接的节点数受总线上的时间延迟和电气负载限制。

- 符合OSI通信系统参考模型,属于物理层和数据链路层。两线式总线结构,电气信号为差分式,通信介质可以采用双绞线,同轴电缆和光导纤维,一般采用双绞线。

- 总线电平:显性(Dominant): 0, 隐性(Recessive): 1, CAN总线的信号电平具有线与特性,即显性电平0总是会掩盖隐性电平1,如果不同的节点同时发送显性和隐性电平,总线总是表现出显性电平。只有所有节点发送隐性电平是,总线才表现为隐性。线与特性是CAN总线仲裁机制的电路基础。

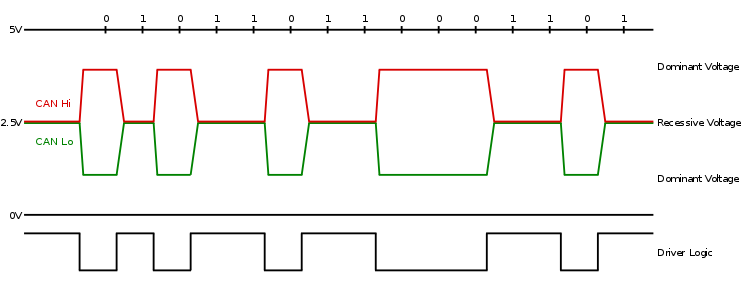

- 高速CAN:总线通信速度最高1Mbp(40m条件下)。高速CAN时,CANH与CANL电压相同时为逻辑“1” (CANH=CANL=2.5V)。CANH和CANL电压相差2V时为逻辑“0” (CANH=3.5V, CANL=1.5V)。高速CAN收发器在共模电压范围内(-12V~12V),将CANH和CANL电压差大于0.9V成为显性状态,将CANH和CANL电压差小于0.5定义为隐性状态。

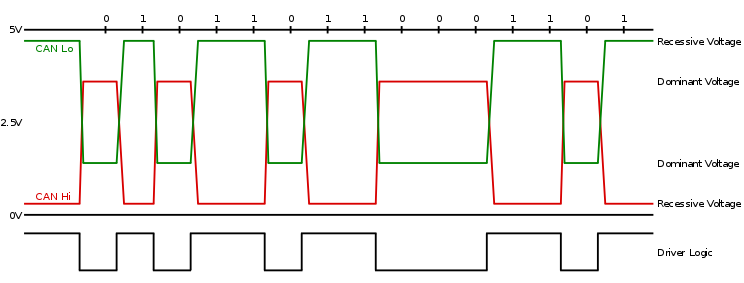

- 低速CAN:定义CANH和CANL电压相差 5V (CANH = 0V, CANL = 5V)时为逻辑“1”,相差 2.2V (CANH = 3.6V, CANL = 1.4V)时为逻辑“0”。

CAN报文帧结构:在CAN总线上,报文以“帧”的形式发送,每个报文帧包含以下部分:

- 帧起始:总线空闲时为隐性状态,帧起始由单个显性位构成,标志报文开始,在总线上起同步作用。

- 仲裁段:仲裁段由报文的标识符完成,即ID,标准CAN的标识符为11位,扩展CAN中为29位。

- 控制段:主要定义了数据域的字节长度,通过数据长度码,接收节点可以判断报文数据是否完整。

- 数据域:主要包含0~8个字节数据。

- CRC域:循环冗余码校验

- 帧结束:由一串七个隐性位组成,表示报文帧的结束。

CAN报文帧种类

(1)数据帧:由发送节点发出,包含0 - 8个数据字节。

(2)远程帧:发送远程帧向网络节点请求发送某一标识符的数据帧。

(3)错误帧:总线节点发现错误时,以错误帧的方式通知网络上的其他节点。

(4)过载帧:发送过载帧,表示当前节点不能处理后续的报文(如帧延迟等)。

SPI协议

SPI(Serial Peripheral interface)串行外围设备接口,该接口主要用在EEPROM,Flash,实时时钟,AD转化器,数字信号处理器和数字信号解码器之间。

- 该协议是一种高速的,全双工同步串行通信总线。

- 没有速度限制,一般可达到10Mbps。

- 主要有四根线:MOSI, MISO,SCLK,CS(片选,选择从设备)。数据在上升下降沿改变。

- 优点:全双工通信,简单,传输速率快

- 缺点:没有指定的流控制,没有应答机制确认是否收到数据,相对IIC可靠性不高。

- SPI的四种模式:

SPI有四种工作模式,SPI为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟的极性(CPOL)和时钟相位(CPHA)可以进行配置。CPOL决定SPI空闲时,时钟信号的电平。CPHA决定SPI在SCLK的第几个边沿开始采样数据。

- CPOL=0:串行同步时钟的空闲状态是低电平

- CPOL=1:串行同步时钟的空闲状态是高电平

- CPHA=0:SPI在串行同步时钟的第一个跳边沿开始采样

- CPHA=1:SPI在串行同步时钟的第二个跳边沿开始采样

DMA

DMA(Direct Memory Access),即直接存储器访问,DMA的传输方式可以无需CPU直接进行控制传输,也没有中断处理方式那样的保护现场和恢复现场的过程。通过硬件为RAM与I/O设备开辟一条直接传输数据的通路,可以使CPU的效率大为提高。

- 作用: 用于内存和内存之间或内存和外设之间的高速数据传输。

- DMA传输包括哪些操作?(STM32为例)

每一次DMA传输包括三个操作- 通过DMA的寄存器寻址,从外设数据寄存器或存储器单元加载数据。

- DMA计数器在数据存储结束后递减,该计算器中包含仍需执行的事务数目。

产生事件后,外设会向DMA控制器发送请求信号,DMA控制器根据通道优先级处理该请求,只要DMA控制器访问外设,DMA控制器就会向外设发送确认信号,外设获得确认信号后,便会立即释放请求。一旦外设使请求失效,DMA就会释放确认信号。如果有更多的请求,外设可以启动下一个事务。

C语言

Static关键字作用

Const关键字作用

Voilatile关键字作用

install_url to use ShareThis. Please set it in _config.yml.